电路基础

- 器件基础

- 基本电路术语与符号

- 信号浮动

- 三态门(三态缓冲器)

- 上下拉电阻

- 基本元件与逻辑

- OC/OD门(掌握原理,用途)

- 开放收集器(OC门,NPN型三极管)掌握原理、用途

- 漏极开路(Open Drain,OD)

- 推挽电路

- 退耦与旁路

- 驱动过载

器件基础

芯片(chip):半导体材料制成的电路器件;

引脚(lead):半导体器件和外部连接的部分,排布在芯片两侧或四周

封装(packaging):将半导体器件以特定方式、特定材料包装起来,提高可靠性、便于使用;

数据表(datasheet):芯片制造商提供的关于产品信息的文档,说明了芯片的功能

印制电路板(printed circuit board,PCB):薄的纤维玻璃板,印有铜线来连接元器件;

原理图(schematic diagram):表示电路的主要部分及元件之间的连接

思考:从器件的封装,延伸如何用器件构造系统?

如何用其设计系统?需要哪些组件和技术?

电器特性、引脚功能、接口形式、使用方法。

核心思想:硬件设计与软件设计、搭积木

共性方法:部件库(积木部件/元件库/函数库) + 逻辑组装 + 设计工具

基本电路术语与符号

接地电压/低电平:0V电压;

接地引脚(GND):接到一直时低电平的信号;

集电极电压/高电平:3V、5V、12V电压

任何时候,电路中的信号要么高要么低

电路供电电压Vcc、芯片工作电压Vdd、发射极电源电压Vee、编程电压Vpp

TTL电平:TTL器件+5V,高电平为逻辑“1”,低电平为逻辑“0”;

输出L: < 0.8V; H:> 2.4V;

输入L: < 1.2V; H: > 2.0V;

CMOS电平:CMOS器件12V,高电平为逻辑“1”,低电平为逻辑“0”;

输出L: < 0.1Vcc; H: > 0.9Vcc;

输入L: < 0.3Vcc; H: > 0.7Vcc;

RS-232电平:负逻辑电平,即负电平 -3到-12V为逻辑“1”,正电平+3到12V为逻辑“0”;

实际设计中,可以搭电路或采用专用器件进行不同电平的转换。

信号浮动

信号:是时-空域中,以特定载体(如光、电、声音等)和特定形式传输信息的能量单元;是信息的物理表示;

浮动信号(多驱动信号)

下图中如果没有任何输出信号,会有什么问题?

没有驱动,信号可能高也可能低,或者处于二者之间某个状态(浮动)——>依赖于信号两端元件的瞬时状态,无法预见;

下图中,如果任何一个选择信号都不是有效,会有什么问题?

信号浮动

如何解决:安装一个辅助元件来驱动其高低——>上拉电阻、下拉电阻;

三态门(三态缓冲器)

可以将信号驱动为高电压、低电压、浮动状态;

浮动状态即第三种输出状态,也称三态、高阻抗态;此时既不像输出0状态那样允许电流灌入,也不象输出1状态那样向负载提供电流,处于悬浮状态

用于多个数据源共享一根(组)线路,驱动同一信号。

上下拉电阻

上拉电阻(Pull-up resistor):连接在元件信号引脚和高电平之间的电阻,用于将引脚信号钳位在高电平,或在驱动能力不足时提供电流。

通常其值可在1千欧到100千欧之间,值越大输出电平的延迟越大;值越小,电流越大,上拉能力越强,但损耗越大:V✖I。

基本元件与逻辑

三极管(Bip Transistor,双极性结型晶体管)

有三个极,三个极分别为N型与P型组成;

作为一种可变电流开关,能够基于输入电压控制输出电流;

晶体管是电流控制元件。

场效应管(Field Effect Transistor,FET场效应晶体管)

利用控制输入回路的电场效应来控制输出回路电流的半导体器件;

场效应管是电压控制器件。

集成电路中,二者都抽象为为开关,向上支持逻辑门设计。

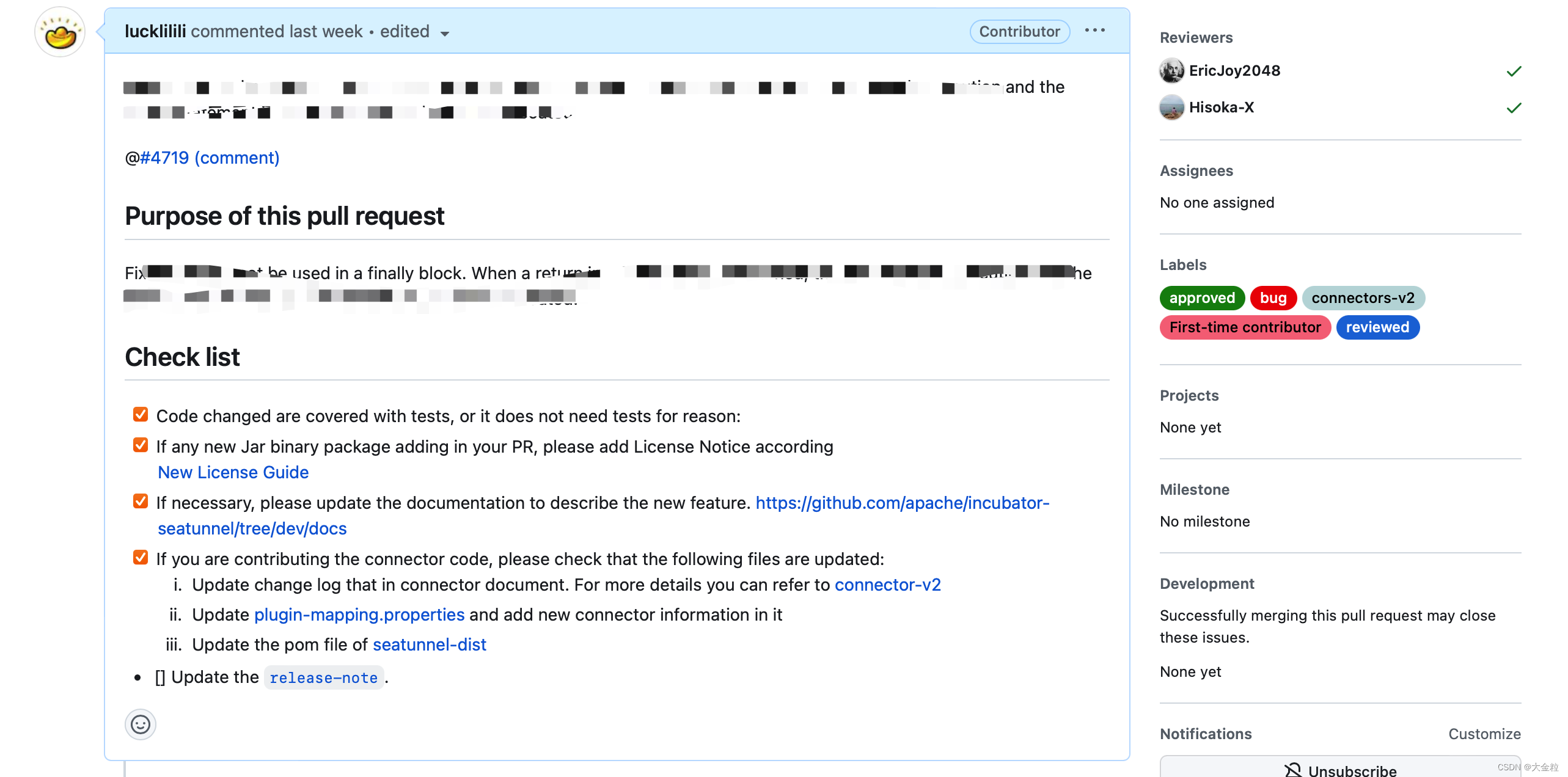

OC/OD门(掌握原理,用途)

开放收集器(OC门,NPN型三极管)掌握原理、用途

输出装置,实际为NPN型三极管;即可驱动输出,也可以处在高低电压

不定状态;

多个这种输出连接到同一信号上,只要一个为低电压,该信号就变为低

电压; 解决了总线竞争问题;

如两个外设向CPU发出中断请求,

示例:NPN开放收集器输出的结构

示例:开放收集器7407工作原理

漏极开路(Open Drain,OD)

N-MOS场效应管,漏极浮空;

在I/O向栅极供电时导通并“漏”电流(吸收电流),输出低电平;

也可以支持多个开漏输出引脚的“线与”连接。

推挽电路

常使用一对参数相同的功率三极管或MOSFET管,以推挽方式存在于电路中;

由图采用了两个互补的增强型MOSFET,顶部是P-MOS场效应管(Top-Transistor),底部是N-MOS场效应管

(Bottom-Transistor)。

多个OC型推挽电路不能进行“线与”型的逻辑操作,一条总线上只能有一个推挽输出器件,为什么?

两个OC输出同时驱动一个信号时,若驱动不一致则可能导致元件被烧坏,乃至系统瘫痪;这个问题是由电路设计错误造成的。

![[PCIE703]FPGA实时处理器-XCKU060+ARM(华为海思视频处理器-HI3531DV200)高性能综合视频图像处理平台设计资料及原理图分享](https://img-blog.csdnimg.cn/f62c233b747e4d968d03c33ceffb7bec.png)